# Presentation Investigation of a Comparator Constructed Mixed-signal Control Loop in 28 nm CMOS

Y. Sravan Kumar<sup>1</sup>, Aleti Soumya<sup>2</sup>, MD. Bilal<sup>3</sup>, M. Ganesh Kumar<sup>4</sup>, K. Salomi Monica<sup>5</sup>

<sup>1</sup>Associate Professor, Sreyas Institute of Engineering and Technology, Nagole, Hyderabad, Telangana. E-mail: y.sravan16@gmail.com

<sup>2</sup>Assistant Professor, St. Martin's Engineering College, Kompally, Secunderabad, Telangana. E-mail: soumyayadama@gmail.com

<sup>3</sup>Assistant Professor, SVR Engineering College, Nandyal, Kurnool, Andhra Pradesh. E-mail: 404bilal@gmail.com

<sup>4</sup>Assistant Professor, SVR Engineering College, Nandyal, Kurnool, Andhra Pradesh. E-mail: mgani411@gmail.com <sup>5</sup>Assistant Professor, MLR Institute of Technology, Hyderabad, Telangana.

E-mail: monicasalomi2014@gmail.com@gmail.com

Abstract: In differential flagging frameworks utilizing copper supports normal method signals remain the reason for absolution of electromagnetic vitality. Particularly fashionable Self-propelled Ethernet frameworks this remains a difficult issue. Adjacent to ancient grace aloof segments like regular mode stifles dynamic circuits can assist with lessening the outflow. This permits economical and asset rationing unshielded curved pair links towards remain utilized. This paper demonstrations the methodology of utilizing a blended sign controller circle dependent proceeding a comparator besides a 8 quantity DAC designed aimed at managing the basic approach voltage of an Automotive Ethernet DAC popular 28 nm CMOS. A constriction meant aimed at interface through frequencies active towards 500 kHz stands accomplished also comes to up to 15 dB by greatest. The control circle uses the progressive guess calculation normally utilized for delay bolted circles and DC tending to in blended sign circuits. Rather than known requests the presentation then convenience at higher frequencies stands measured now this paper. Existence a non-straight, time-variation framework a logical structure of the switch circle is actual difficult. In future parametrical calculations protest the reliance of reappearance, abundance also sign grouping of a practical elementary manner interferer substance.

Keywords: Successive Approximation Register (SAR), Digital Control, Nonlinear Control, Automotive Ethernet.

# 1. INTRODUCTION

Electromagnetic similarity remains a significant piece of Auto-rationale Microchip technology. Fast Automotive Ethernet joins comparable 1000BASE-T1 through a data communication375 MHz stand intended towards utilize difference motioning finished curved couples copper shapes. Normal manner signals happening these lines possibly will make radiation outer connections and be touchy to their radiation. Towards adapt these issue inactive gadgets corresponding basic method gags before costly protected pairs associations remain generally utilized. These paper offerings a blended sign regular mode control circle

intended for a 6 piece DAC utilized trendy an Automotive Ethernet carnal coating IC designed aimed at 1000BASE-T1. Over this methodology a functioning concealment of regular approach voltages remains conceivable. Existence executed fashionable 28 nm CMOS innovation the plan of additional segments similar an operative amplifier designed used aimed on a modest normal manner circle can remain effortful. Since in general soundness must be kept up, this functioning amplifier requirements a pay capacitor which can remain actual enormous besides consequently costly in an exceptionally mounted innovation.

Executing a regular blended sign control circle which necessitates an ADC designed for estimating the framework yield individually the mistake signal. Through diminishing cycle skills size structuring an ADC gets all the more testing. This methodology rather uses a 1 portion ADC (comparator) which facilitates the plan cycle. Next to this likewise a non-direct simple exchange work is conceivable to manage. This paper is impelled through preparations recognized after postponement fastened circles anywhere a Consecutive Estimate Record is exploited towards accomplish a multi-bit harvest through an a combine of bit contribution [1]. Significant execution boundaries are fastening time besides jitter. Certainly, even in continuing history enhancements for this SAR-approach remain distributed fashionable the field of DLL [2]. Fashionable [3] the SAR-calculation is utilized designed for overall DC predisposition tending to trendy blended sign routes. As opposed to effectively executed blended sign control circles dependent on a comparator contribution this paper assesses the convenience as well execution at advanced frequencies. In area II the hypothesis in calculation advanced execution is designated tracked through the combination fashionable the Automotive Ethernet DAC popular segment III. Calculation consequences of the blended sign control circle directing the Automotive Ethernet DAC basic approach voltage remain originate fashionable segment IV.

### 2. REGULATOR HOOP METHOD

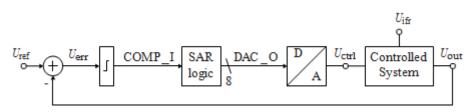

As per a standard control round the introduced approach appeared in figure 1 comprises of a simple controlled framework, a deduction of the orientation esteem Uref on or after the framework yield Uout and a Consecutive Estimate Catalogue rationale which computes the control indication Uctrl so as to eliminate the influence of the meddling sign Uifr.

Fig. 1 Control loop block level

Attractive absent Uout from Uref is unquestionably complete through the comparator which stretches a produce of 1 if Uout is better than Uref = 800 mV besides 0 in some case. The alteration towards direct working control circles is that the control indicator Uctrl remains certifiably not a direct estimation of the mistake indication Uerr. Somewhat the info sign of the regulator is resolute through a SAR-calculation. It utilizes the parallel comparator contribution COMP I by way of information besides gives an 8 piece transport DAC O. In this way an enormous mistake signal prompts a similar impact comparable a slight unique at the first timer sequences. For both situations the comparator consumes a similar worth. So as to give a dressed guideline data transfer capacity by a quick evacuation even of quick rising

or huge Uerr quite a while of equivalent requirements COMP I is meant an enormous difference in DAC O.

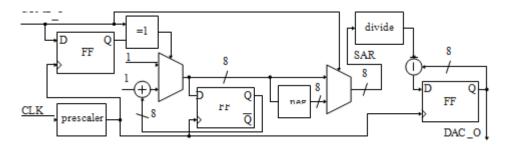

Fig. 2 SAR logic schematic

In figure 2 the diagram of the computerized share remains looked. The sign COMP\_I remains hooked besides contrasted with the ancient worth. On the off chance that a alteration happens the inner 8 portion catalogue is rested to 1. Contingent upon COMP I the register esteem remains refuted before not bringing about the sign SAR. Separating signal SAR gives a decrease of clamor defencelessness through moving towards one side through a adjustable worth. An integrator circuit summarizes the separated symbol SAR towards DAC O inside limitations of an 8 portion transport. Soaking rationale restricts overflow at lower and furthest cut-off points.

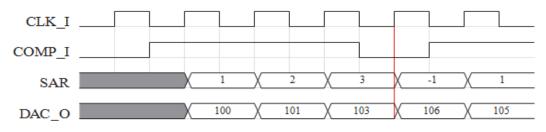

Fig. 3 Regulator loop worth SAR besides DAC O designed for an instance comparator contribution arrangement

It shows demonstrations the count of SAR designed for a model info succession of COMP I. The comparator indication remains locked on the increasing advantage of CLK I. On both after clock i[iround a stage thickness remains added to DAC O. The progression thickness is at first 1 besides remainders progressively expanded if COMP I remains consistent. This prompts an exponential increment before diminishing of DAC O designed for persevering mistakes which principal towards a consistent info COMP I. On the off chance that COMP I fluctuations, the progression thickness is rested to 1 or - 1. Cutting-edge the model appeared in figure 3 a division factor of 1 then a prescaler estimation of 1 is utilized. This prescaler permits defining the control circle clock recurrence. In the event of a steady interferer Uifr the sign Uctrl ought to likewise be consistent. Despite the fact that this methodology needs a flipping COMP I sign to keep up a consistent Uctrl. In any case the SAR calculation has no data how far the framework yield Uout is away from the focused on reference Uref. Best case scenario the consistent state swell is 1 DAC LSB. The LSB scope can remain usual toward a worth little sufficient that trustworthy formal wave can be dismissed. Alongside the control circle DAC LSB scope the f-3 dB transmission capacity of the skilful framework can be planned. Scheduled the computerized lateral the main two locations are the clock presales then the separation factor which defines in what way quick the progression breadth raises.

The guideline nature of this methodology remains subject to adequacy, recurrence and sign type of the interferer Uifr. While moderate rising interferers can be taken out totally quick increasing interferer's principal to an overrun for a similar switch circle plan. In the event that the recurrence of the interferer is enormous appropriate the lessening gave through the control circle drips towards zero before smooth towards negative qualities. The circuit appeared popular figure 2 remained actualized in 28 nm CMOS innovation along through the measured framework portrayed trendy the accompanying section.

#### 3. SUBMISSION OF THE CONTROL TWIST

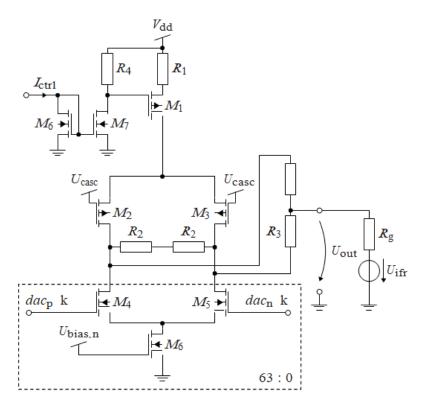

As self-possessed framework intended aimed at the introduced regulator circle technique a 6 portion DAC aimed at 1000BASE-T1 Automotive Ethernet work fashionable 28 nm CMOS innovation remained functional. This 6 portion DAC gives a difference yield sign of -1 V to +1 V into a difference heap of 50  $\Omega$  besides uses a present directing engineering through 64 unary compartments. In figure 4 the total yield phase is looked. The heap resistors R2 of the 6 piece current controlling DAC remain executed scheduled chip. The framework through dual related animal coating ICs (PHY) is resistively showed through R3 which remain putting on PCB. R2 besides R3 corresponding 50  $\Omega$ .

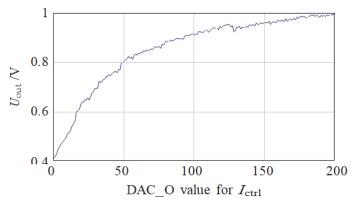

Fig. 4 Diagram of 6 bit DAC production phase applied in 28 nm CMOS Technology. Mutual manner voltage Uout be situated measured through current Ictrl. Indicator producer provender interfering signal Uifr into the mutual approach voltage Uout

The controlled sign remains the regular method yield voltage Uout appeared in figure 4. As indicated through the frontend structure a typical method voltage of 800 mV remains focused on. A most extreme concealment of several AC sign of the basic approach voltage Uout prompts least discharge of radiation and affectability to radioactivity of electromagnetic

sprays finished the curved couple's link. This is urgent designed for strong correspondence in automotive condition.

Fig. 5 Slow transfer purpose as of regulator loop DAC which produces current Ictrl to mutual manner voltage Uout

# 4. CAPACITIES

#### A. Quantity Operation

The approximations of the framework depicted in areas II besides III remained finished utilizing a Python constructed computerization content. Designed for producing Uifra Key sight 33600 sign producer remained utilized. Because of various sign structures the top to-top amplitudes remain measured designed on behalf of the examination of the switch circle conduct. A RTO-1044 oscilloscope remained utilized towards quantify the subsequent regular style voltage Uout. To portray the control circle implementation AC measurements of Uout were finished. Its top to-top abundance is defined by way of Upp,cm besides his standard unconventionality by way of  $\sigma$  cm. Designed for exhibiting the non-straight conduct of the control circle various boundaries remained thought about. As a sensible amount the constriction a cm beginning Upp,cm of the handicapped control circle to Upp,cm of the empowered control circle remains defined as appeared popular condition (1).

$$a_{\rm cm} = \frac{U_{\rm pp,cm}|_{\rm disabled \, loop}}{U_{\rm pp,cm}|_{\rm enabled \, loop}} \tag{1}$$

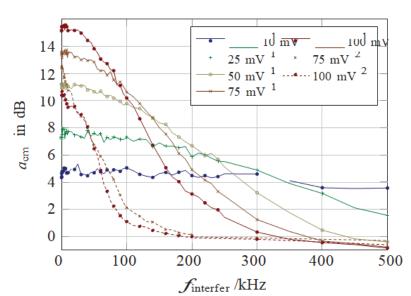

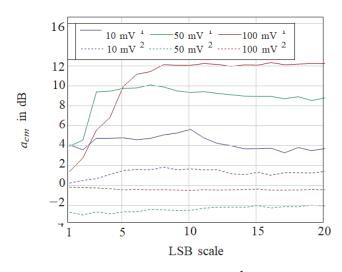

Fig. 6 Restrained mutual mode reduction for functional sinusoidal interferer through peakto-peak amplitudes of Upp,ifr = 10 mV to Upp,ifr

# **B.** Offsetting Dimensions Finished Frequency

The non-straight conduct can be understood popular figure 6 intended for a sinusoidal interferer through various top to-top amplitudes Upp,ifr as of 10 mV towards 100 mV. Though a little meddling signs through Upp,ifr = 10 mV need an about consistent lessening  $a_{cm}$  over recurrence, bigger Upp, ifr principal towards a solid recurrence reliance. This remains an impact of the SAR rationale steadily expanding the progression width while a quick increasing meddling sign Uifr is applied. At most extreme a lessening  $a_{cm}$  of 15 dB is gone after Upp,ifr = 100 mV by little frequencies. Meanwhile of the clamor floor, tinier estimates of Upp, ifr major to slighter weakening assets. As referenced in segment II little meddling signs can be weakened up to from top to bottom frequencies of 500 kHz. Adjacent to the non-direct conduct contingent upon interferer top to-top adequacy diagram 6 shows the effect of the control circle LSB size. Utilizing five occasions the negligible LSB magnitude prompts an development of 9 dB if there should be an occurrence of a sinusoidal interferer through Upp,ifr = 100 mV besides a recurrence of 100 kHz. A nitty gritty examination of the influence of LSB size on Upp, cm shadows in segment IV-C.

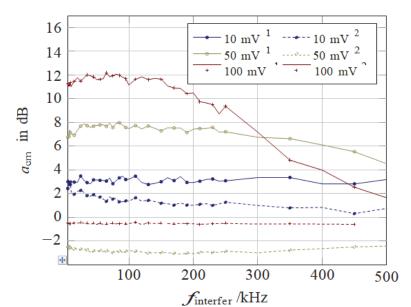

It shows demonstrations the switch circle execution by means of a component of the data transfer capacity of a functional repetitive sound. As opposed to the sinusoidal interferer the most extreme weakening is lower however a smaller amount recurrence subordinates. Intended for incidence a sinusoidal interferer finished a re-emergence of 500 kHz and Upp,ifr = 50 mV is patterned finished 1.5 dB though an uninteresting sound through a data transmission capacity of 500 kHz is restrained through 4.5 dB. Giving the quickest ascent time then huge Upp, ifr the square wave interferer remains ineffectively constricted as figure 7 demonstrations. Upp, ifr of 50 mV or all the additional smooth principal towards an expansion of the deliberate abundancy Upp, cm if the control circle becomes empowered. Accordingly the constriction  $a_{\rm cm}$  intended for such square-wave interferer's remains undesirable.

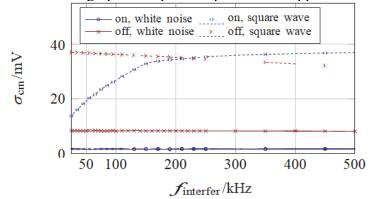

Anyway there stands a development of the normal unorthodoxy by way of figure 8 demonstrations intended for the instance of Upp, ifr = 100 mV. Despite the fact that the top to-top plentifulness expands the left over interferer vitality is diminished if the square wave recurrence remains under 200 kHz. If there should be an occurrence of a repetitive sound a consistent decrease of the normal unconventionality is given up to 500 kHz.

# European Journal of Molecular & Clinical Medicine ISSN 2515-8260 Volume 7, Issue 11, 2020

Fig. 7 Slow mutual mode weakening for functional 1 white noise then 2 tetragonal wave interferer through peak-to-peak amplitudes of Upp, if r = 10 mV

Fig. 8 Restrained common style normal deviation for white noise then square wave interferer through 100 kHz. Judgment of enabled and inactivated control twist.

#### C. Reduction Capacities completed Control Twist LSB Size

Attenuation is look as if in figure 9 which gives a plot of  $a_{cm}$  by means of an element of the switch circle LSB magnitude. On the off chance that the LSB size is to little a huge sufficiency Upp,cm lives particularly for huge Upp,ifr. By an expansion more than multiple periods the base doesn't prompt additional development of the constriction. The lessening of square wave interferers possibly improvement after a bigger control circle LSB scope if the top to-top plentifulness remains by most extreme 50 mV. Background noise indications demonstration a similar conduct as sinusoidal interferers.

#### 5. CONCLUSION

In this paper a methodology designed aimed at a blended sign regulator circle recognized after different fields remained used for the normal style guideline of an Automotive Ethernet current directing DAC.

Fig. 9 Restrained shared mode reduction for practical <sup>1</sup>sinusoidal besides <sup>2</sup>square wave interferer through amplitudes of *U*<sub>pp</sub>,ifr=10mV, *U*<sub>pp</sub>,ifr=50mV in addition

Numerous approximations show the reliance of the control circle execution described by the constriction  $a_{cm}$  on the meddling sign. Close to the recurrence of the interferer its top totop sufficiency Upp,ifr and sign structure has incredible effect on  $a_{cm}$ . While sinusoidal interferers besides repetitive sound are weakened active to 500 kHz besides awake to 15 dB square wave interferers remain inadequately lessened. Impartial square wave interferers through an adequacy by way of stumpy by means of Upp,ifr = 10 mV are declining by 3 dB in this framework. All things considered the control circle gives a constriction to a few meddling sign sorts and a simple alteration to novel frameworks. Calculation a low pass filter towards the comparator would recover the exhibition through having the option in the direction of diminish the high essential division factor of 26 which diminishes the weakening at higher interferer frequencies despite the fact that a framework clock of 100 MHz besides presale of 1 remains utilized. In any case the proposed control circle gives great presentation in the assumed request and can be moved to extra measured frameworks through non-direct exchange work absent a lot of exertion.

#### 6. **REFERENCES**

- [1] Guang-Kaai Dehng, Jyh-Woei Lin, Shen-Iuan Liu "A fast-lock mixed-mode DLL using a 2-b SAR algorithm," *IEEE Journal of Solid-State Circuits*, vol. 36, Issue. 10, pp.1464– 1471, Oct 2001.

- [2] Ko-Chi Kuo, Sz-Hsien Li, "A wide-range and harmonic-free SAR all-digital delay locked loop," in 2015 15<sup>th</sup> *International Symposium on Communications and Information Technologies (ISCIT)*, Oct 2015, pp.197–200.

- [3] Laszlo Szilagyi, Jan Pliva, Ronny Henker, David Schoeniger, Jaroslaw P. Turkiewicz, and Frank Ellinger, "A 53-Gbit/s optical receiver frontend with 0.65pJ/bit in 28- nm bulk-cmos," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 845–855, March 2019.

- [4] Yijun Wang, Tzyy-Ping Jung, "A Collaborative Brain-Computer Interface for Improving Human Performance," *PLoS ONE*, vol.6, no.5, May 2011.

- [5] Adrian Stoica, Ana Matran-Fernandez, Dimitrios Andreou, Riccardo Poli, Caterina Cinel, Yumi Iwashita, Curtis W Padgett, "Multi-brain fusion and applications to intelligence analysis," in *Proceedings of SPIE*, Vol: 8756, Baltimore, Maryland, 2013.

- [6] Ana Matran-Fernandez, Riccardo Poli, Caterina Cinel, "Collaborative brain- computer interfaces for the automatic classification of images," in Neural Engineering (NER), 2013 6<sup>th</sup> International IEEE/EMBS Conference on. San Diego (CA): IEEE, 6–8 November 2013, pp.1096–1099.

- [7] Peng Yuan, Yijun Wang, Wei Wu, Honglai Xu, Xiaorong Gao, Shangkai Gao, "Study on an online collaborative BCI to accelerate response to visual targets," in *Annual International Conference of the IEEE Engineering in Medicine and Biology Society*. 2012, pp.1736–1739.

- [8] Riccardo Poli, Caterina Cinel, Francisco Sepulveda, Adrian Stoica, "Improving Decision- making based on Visual Perception via a Collaborative Brain-Computer Interface," in *IEEE International Multi-Disciplinary Conference on Cognative Methods in Situation Awareness and Decision Support (CogSIMA).* San Diego, CA, USA: IEEE, February 2013.

- [9] A.D. Gerson, L.C. Parra, P. Sajda, "Cortically coupled computer vision for rapid image search," *IEEE transactions on neural systems and rehabilitation engineering*, vol.14, no.2, pp.174–179, Jun.2006.

- [10] Amy Kruse, Scott Makeig, "Phase I analysis report for UCSD/SoCal NIA team," Institute for Neural Computation, University of California San Diego, LaJolla, Tech. Rep. January, 2007.